主页 > imtoken苹果版官网下载 > 比特流缓冲控制器及其控制方法

比特流缓冲控制器及其控制方法

比特流缓冲控制器及其控制方法

技术领域

[0001] 本发明涉及一种视频解码器,更具体地,涉及一种用于H.264/AVC解码器的比特流缓冲控制器及其控制方法。

背景技术

[0002] FIFO缓冲器通常用于视频解码器的比特流控制器中,用于临时存储和流控制,并且通常用作读写指针的循环队列。前面的读写指针都是同一个内存位置,FIFO队列为空。像往常一样,视频解码器必须先查询FIFO空状态,以保证每次读取数据时存储的数据的正确性,这样会降低视频解码器的效率。

[0003] 因此,当前的需要是提供一种能够减少视频解码器的FIFO空状态的不必要排队的比特流缓冲控制器。·

发明内容

[0004] 本发明提供一种具有可变比特流空状态检查模块的高效比特流缓冲器控制器。

一种用于视频解码器的码流缓存控制器,包括第一FIFO缓存、第二FIFO缓存和中断控制器,第一FIFO缓存用于存储输入码流,第二FIFO缓存用于存储有效载荷,其中有效载荷取自输入比特流,中断控制器根据第一个 FIFO 缓冲区和第二个 FIFO 缓冲区的满状态产生一个中断信号,这样每次加载有效载荷时,视频解码器可以切换加载有效载荷而不检查饱满状态。

一种用于视频解码器的比特流缓冲区控制方法,包括:接收并存储第一FIFO缓冲区的输入比特流,获取并存储有效载荷,所述有效载荷取自输出缓冲区中的输入比特流的第二FIFO,以及根据第一FIFO缓冲器和第二FIFO缓冲器的满状态产生中断信号,使视频解码器在检查和未检查模式之间切换,加载有效载荷,从而可以降低检查满状态的频率。

本发明通过产生适当的中断信号并维护SW功能指示符,有助于让处理器只要触发中断就可以检查指示符状态,即比特流不需要确认FIFO的状态指示符缓冲。被访问,从而达到提高进程性能的效果。

前述段落概述了本发明的特征和技术优点。为了能够更清楚地理解本发明的详细描述,本发明的其他特征和优点将在以下描述中公开。

图纸说明

下面对附图和附图进行简要说明,从而更全面地揭示本发明的细节和优点:

[0010] 图。附图说明图1是表示本发明的一个实施方式的比特流缓冲控制器的结构的框图。

[0011] 图。图2是示出图1的比特流缓冲器控制器的控制信号和数据流的细节的框图。1.

[0012] 图。图3是示出图1的比特流缓冲器控制器的操作的流程图。1.

[0013]【主要成分符号说明】

100比特流缓冲控制器

101视频解码器

102外部存储器

103内存接口

104 位流 FIFO 缓冲器

105进程管理器

107 打包的基本比特流解析器

108网络抽象层单元到原始字节序列有效负载的解析器

109 原始字节序列加载先入先出缓冲区

110中断控制器

112 位流管理器

201比特流缓冲控制器

202 多台设备

301、302、303、304、305 步

详细方法

[0028] 以下对本发明实施例的相关描述均与本发明的附图相关。

图1是示出根据本发明实施例的比特流缓冲器控制器100的配置的框图。比特流缓冲器控制器100可以避免不必要地检查FIFO缓冲器空状态,例如用于H.264/AVC解码器。

位流缓冲器控制器100包括存储器接口103、位流先进先出缓冲器(BSB FIFO;位流缓冲器先进先出)104、进程管理器105、Packetized Elementary Stream Parser (PES parser; Packetized Elementary Stream Parser) 107、Network AbstractLayer Unit to Raw Byte Sequence Payload (NALU2RBSP; Network AbstractLayer Unit to Raw Byte Sequence Payload) parser 10 8、 raw字节序列加载先进先出缓冲器(RBSP FIFO;原始字节序列分组先进先出)109、中断控制器110和位流管理器112。比特流缓冲控制器100用于接收比特流,比特流或者是打包的基本比特流的形式,或者是基本比特流的形式,例如外部存储器102,并且位流缓冲控制器100还用于输出中断信号,这使得视频解码器101能够以检查或未检查模式获取位流并将其存储在RBSP FIFO 109中。在检查模式中,每次视频解码器101加载存储在RBSPFIF0 109中的原始字节序列有效载荷时,视频解码器101检查RBSP FIFO 109的充满度;当视频解码器101加载存储在RBSPFIF0 109中的原始字节序列有效载荷时,视频解码器101不检查RBSP FIFO 109的完整状态。每次视频解码器101加载存储在RBSPFIF0 109中的原始字节序列有效载荷时,视频解码器101检查RBSP FIFO 109的充满度;当视频解码器101加载存储在RBSPFIF0 109中的原始字节序列有效载荷时,视频解码器101不检查RBSP FIFO 109的完整状态。每次视频解码器101加载存储在RBSPFIF0 109中的原始字节序列有效载荷时,视频解码器101检查RBSP FIFO 109的充满度;当视频解码器101加载存储在RBSPFIF0 109中的原始字节序列有效载荷时,视频解码器101不检查RBSP FIFO 109的完整状态。

假设外部存储器102提供比特流,存储器接口103通过BSB FIFO 104连接到外部存储器102,进程管理器105控制BSB FIFO 104加载比特流,比特流要么在基本比特流的形式或分组化的基本比特流形式,其中比特流通过存储器接口103从外部存储器102加载。另外,外部存储器102优选地是双倍数据速率同步动态随机存取存储器(DDR SDRAM ;双倍数据速率同步动态随机存取存储器),并且外部存储器102由双倍数据速率同步动态随机存取存储器控制器(DDR控制器)控制(图中未示出)。在一个实施例中,

打包基本比特流解析器107用于:如果存储在BSB FIFO 104中的比特流是打包基本比特流的形式,则打包基本比特流解析器107存储在BSB FIFO中的比特流中104 获得基本比特流格式有效载荷;在一个替代实施例中,如果存储在BSB FIFO 104中的比特流是打包的基本比特流格式,则打包的基本比特流解析器107也可以将输入的比特流绕过到下一级,即NALU2RBSP的解析器108。在本实施例中,打包的基本比特流解析器107还可以通过打包的基本比特流的形式获得比特流中的呈现时间戳(PTS;Presentation Time Stamp)信息比特流谁发明的,用于后续的视频解码过程。

RBSP FIFO 109用于加载NALU2RBSP的解析器108得到的原始字节序列加载,在本实施例中,RBSP FIFO 109可以生成第二索引,该第二索引可以指示五种RBSP FIFO 109。不同的状态,即空、几乎空、半满、几乎满、满状态等,在替代实施例中,第一指示符可以指示RBSP FIFO 109的更多或更少种类的状态。

[0035] 此外,比特流管理器112用于根据语法规范将存储在RBSP FIFO 109中的原始字节序列有效载荷去转换到视频解码器101。

中断控制器110用于减少检查视频解码器101的FIFO空状态的不必要过程。在本实施例中,中断控制器110用于产生中断信号,使得视频解码器101处于检查模式. 或未检查模式以加载存储在RBSP FIFO 109中的原始字节序列有效载荷。如在该示例中,中断信号可以是用于将视频解码器101切换到检查模式以加载存储的原始字节序列有效载荷的[空]中断信号在RBSP FIFO 109中;或者中断信号可以是[full]中断信号用于将视频解码器101切换到未检查模式以加载存储在RBSP FIFO 109中的原始字节序列有效载荷。

在[empty]中断信号的示例中,中断控制器110用于检测BSB FIFO 104和RBSP FIFO 109的状态指示符是否达到预设的空配置(empty configuration),如在本示例中比特流谁发明的,预设的空配置可以设计为几乎空的 BSB FIFO 1045 的第一索引,以及几乎空的 RBSP FIFO 109 的第二索引,只有当中断控制器 110 接收到 BSBFIF0 104 和 RBSP FIFO 109 的状态索引,并确认满足 In默认空配置,视频解码器101可以切换到检查模式以加载存储在RBSP FIFO 109中的原始字节序列有效载荷。在关于[full]中断信号的另一个替代实施例中,中断控制器110用于检测BSB FIFO 104和RBSP FIFO 109的状态指示符是否达到预设的满配置,如本例中,预设的满配置可以设计为接近满的第一指示。仅当中断控制器110接收到BSB FIFO 104和RBSP FIFO 109的状态指示符时,BSBFIF0 1045和用于几乎满的RBSP FIFO 109的第二指示符,并且当确认满足预设的完整配置时,视频解码器101可以切换到未检查模式以加载存储在RBSP FIFO 109中的原始字节序列有效载荷。此外,本发明所属领域的任何技术人员都可以理解:

通过将视频解码器 101 适当地切换到未检查模式以加载存储在 RBSPFIF0 109 中的原始字节序列有效负载,从而减少查询 FIFO 状态的频率,在中断控制器 101 和 BSB 的帮助下, FIFO 104 的利用率和RBSP FIFO 109,因此可以大大提高视频解码器101的性能。

图2是示出用于图1的比特流缓冲器控制器100的控制信号和数据流的细节的框图。参照图1,此外,例如,图1的过程管理器105也可以与图1的过程管理器105相结合。图1可以是比特流缓冲器控制器。设备201和多设备202的详细特征公开如下。

位流缓存控制器201调整存取速率使BSB FIFO 104处于满状态,位流缓存控制器201为存储器接口103生成控制协议,然后将位流从外部存储器102加载到BSB FIFO 104,并且比特流是分组化的基本比特流形式或基本比特流形式。如果BSBFIFO 104的状态指示符变满或几乎满了,则比特流缓冲控制器201将根据控制协议中止将比特流从外部存储器102加载到BSB FIFO 104,并且如果BSB的状态指示符FIFO 104变为半满、几乎为空或为空时,比特流缓冲控制器201将根据控制协议请求将比特流从外部存储器102加载到BSB FIFO 104。

多路复用器202连接到BSB FIFO 104或具有NALU2RBSP的解析器108的打包基本比特流解析器107。如上所述,当输入比特流为分组基本比特流形式时,复用器202将存在分组基本比特流格式比特流,分组基本比特流格式比特流存储在BSB FIFO 104中流经打包后的基本比特流解析器107,得到基本比特流格式载荷,然后进入NALU2RBSP的解析器108,得到原始字节序列载荷。在替代实施例中,当输入比特流是基本比特流格式时,多路复用器202将具有存储在BSB FIF 104中并直接流入NALU2RBSP'的基本比特流格式比特流 s 解析器 108 获取原始字节序列有效负载。此外,打包的基本比特流解析器107用于从存储在BSB FIFO 104中的比特流中获得基本比特流格式有效载荷,并且NALU2RBSP解析器108用于去除用于防止仿真的基本比特流格式有效载荷3字节,其中仿真防止3字节的基本比特流形式的有效载荷由打包基本比特流解析器107获得,或者直接存储在BSB FIFO 104中以获得原始字节序列有效载荷,上述技术特征与图1中公开的技术特征相似。1. 多路复用器202用于:如果第二FIFO缓冲器109的状态指示器变得几乎满或满,

[0042] 比特流管理器112读取存储在RBSP FIFO 109中的原始字节序列有效载荷,并且根据语法规范将存储在RBSP FIFO 109中的原始字节序列有效载荷反变换到视频解码器101。

这里的BSB FIFO 104和RBSP FIFO 109除了存储打包后的基本比特流/基本比特流格式比特流和原始字节序列有效载荷外,还用于根据不同的目的来表示比特流,并产生各自的状态指示器(例如:空、几乎空、半满、几乎满或满状态)来指示它们的满状态。BSB FIFO 104和RBSP FIFO 109的状态指示符可以被中断控制器110发送和接收,并用于根据预设产生中断信号,例如[empty]中断信号或[full]中断信号。中断配置,预置中断配置可以是预置空配置或预置满配置,使得视频解码器101可以在检查模式或取消检查模式之间切换以加载存储在RBSP FIFO 109中的原始字节序列加载。在类似的实施例中,本发明所属领域的任何技术人员都可以理解:为了产生中断信号并使BSB FIFO 104和RBSP FIFO 109达到更好的利用,预设的中断配置可以是单独设计。

通过将视频解码器 101 适当地切换到未检查模式以加载存储在 RBSPFIF0 109 中的原始字节序列有效负载,从而减少查询 FIFO 状态的频率,在中断控制器 101 和 BSB 的帮助下, FIFO 104 的利用率和RBSP FIFO 109,因此可以大大提高视频解码器101的性能。

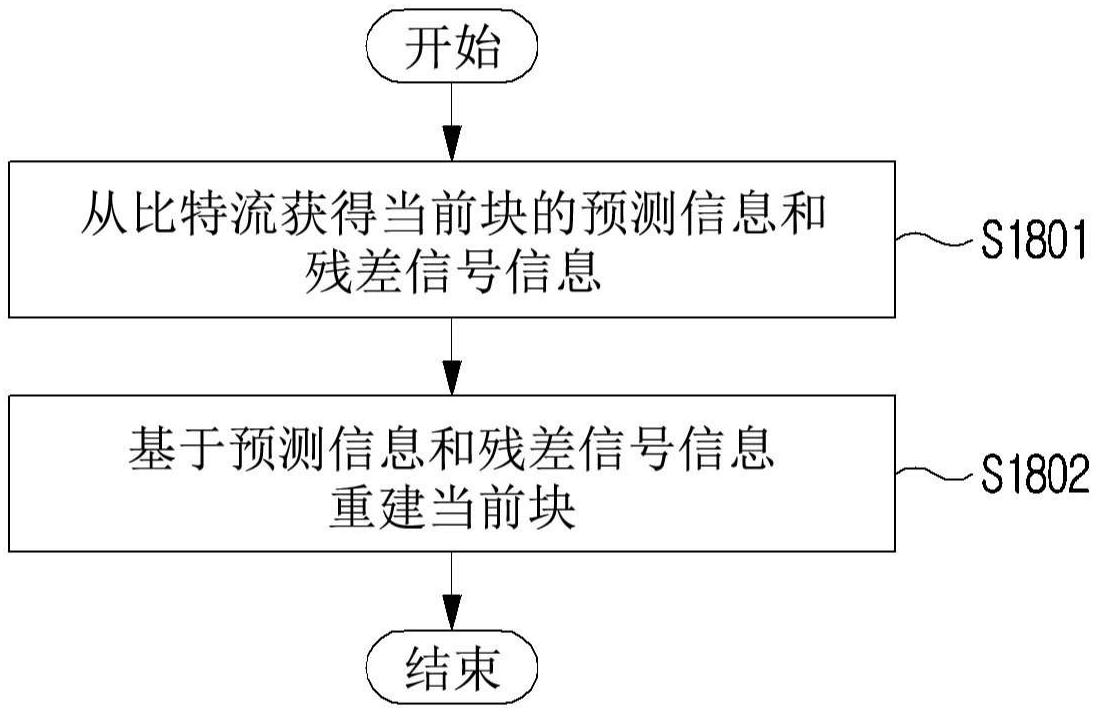

[0045] 图。图3是示出图1的比特流缓冲器控制器100的操作的流程图。1.

关于步骤301,比特流缓冲控制器100处于初始状态,输入比特流存储在BSB FIFO 104中,然后从输入比特流中取出的原始字节序列加载存储在RBSP FIFO 109中,视频解码器101加载在校验模式下存储在RBSPFIF0 109中的原始字节序列有效载荷,即当视频解码器101加载存储在RBSP FIFO 109中的原始字节序列有效载荷时,视频解码器必须在每次101中对RBSP FIFO 109进行一次校验。完整状态指示器,例如,可以通过存储器接口加载比特流。此外,可以根据 BSB FIFO 104 的满状态中止或请求将输入比特流加载到 BSB FIFO 104 的过程,并且将提取的原始字节序列加载到RBSPFIF0 109的过程也可以基于RBSP FIFO 109的完整状态而被暂停或被要求。此外,如果输入比特流是分组基本比特流的形式,则可以解析存储在BSB FIFO 104中的输入比特流以获得基本比特流形式的有效载荷、输入基本比特流形式比特流或获取的基本比特流中的有效载荷可以解析表单以获得原始字节序列有效负载以存储在 RBSPFIF0 109 中。

[0047] 关于步骤302,比特流缓冲器控制器100的中断控制器110检测BSB FIFO 104和RBSPFIFO 109的满状态。

[0048] 关于步骤303,中断控制器110检测BSB FIFO 104和RBSP FIFO 109的满状态是否满足预设的中断配置,例如预设的[空]中断配置或预设的[满]中断配置。

[0049] 接下来,视频解码器101在未检查模式和检查模式之间切换以加载存储在RBSPFIFO 109中的原始字节序列有效载荷,从而降低查询FIFO状态的频率。例如,在步骤304,当中断控制器110检测到BSB FIFO 104和BSP FIFO 109的满状态满足预设的中断配置时,视频解码器101以未检查模式加载存储在RBSP FIFO 109中的数据。原始字节序列加载;相反地,在步骤305,当中断控制器110检测到BSB FIFO 104和BSP FIFO 109的满状态不满足预设中断配置时,视频解码器101将存储在校验模式中的原始字节序列有效载荷加载到RBSP中先进先出 109。

随后返回步骤302和步骤303,这里的比特流缓冲控制器100的中断控制器110再次检测BSB FIFO 104和RBSP FIFO 109的满状态,并检测BSBFIF0 104和RBSP FIFO 109的状态索引是否满足预设中断配置。

视频解码器101在未检查和检查模式之间进行适当的切换,以加载存储在RBSP FIFO 109中的原始字节序列有效载荷,从而降低对FIFO状态的询问频率,并在解码器101的帮助下和利用中断控制BSB FIFO 104和RBSP FIFO 109的组合,可以大大提高视频解码器101的性能。

最后,本发明所属领域的技术人员将会理解,以上描述和实施例仅是本发明示例性和公开的优选实施例和实施细节,并不用于限制本发明的范围,任何技术本发明所属。本领域技术人员应该知道,在不脱离本发明的精神和范围的情况下,可以进行一些变化和修改。因此,本发明的保护范围应以所附权利要求为准。